#기억 장치 계층 (Memory Hierarchy)의 예시

기억 장치의 계층 구성. 즉, 그 동작 속도가 늦은 것에서부터 차례로 자기 테이프 장치, 자기 디스크 장치, 자기 드럼 장치, 자기 버블 장치, CI 장치 등으로 되는데, 이러한 기억 장치의 계층 구성으로 된 시스템을 말한다 또는 캐시, 주기억 장치, 보조 기억 장치 등으로 구분될 수 있다. 쉽게 말해 기억 용량이나 접근 시간의 차이 등을 고려하여 적당히 계층화된 기억 장치. 계층은 고속·소형의 반도체 기억 장치, 중속의 디스크 기억 장치, 대형·저속의 테이프 기억 장치 등으로 구분된다. 또는 캐시, 주기억 장치, 보조 기억 장치 등으로 구분될 수 있다.

#Random-Access Memory (RAM)

RAM / 램이란 사용자가 자유롭게 내용을 읽고 쓰고 지울 수 있는 기억장치이다. 컴퓨터가 켜지는 순간부터 CPU는 연산을 하고 동작에 필요한 모든 내용이 전원이 유지되는 내내 이 기억장치에 저장된다. '주기억장치'로 분류되며 보통 램이 많으면 한번에 많은 일을 할 수 있기에 '책상'에 비유되곤 한다

- 램의 주요 기능

- RAM은 전통적으로 칩으로 포장되어 있다

- 기본 저장 단위는 일반적으로 셀(cell)이다(셀당 1비트)

- 여러 개의 RAM 칩이 메모리를 형성한다

- Static RAM (SRAM)

- 정적 램이라고도 부르며, 내용을 한번 기록하면 전원이 공급되는 한 내용을 그대로 가지고 있는 램이다. 기본적으로 트랜지스터 등으로 구성된 논리 회로로 이루어지며 외부 신호에 따라 내부의 값을 유지하는 식으로 정보를 기록한다. 기억 능력을 가진 논리 회로를 특별히 플립플롭 이라고 부른다. (Flip-Flop: 기초적인 원리는 입력을 받으면 그 입력을 초기화 명령을 받기 전까지 내부에서 루프를 돌려서 유지하는 것 / 외부의 에너지 공급이 없으면 에너지 손실로 빠른 시간 안에 정지.).

- 각 셀은 4개 또는 6개의 트랜지스터 회로를 가진 비트를 저장한다

- 위해도 말했듯이 전원이 켜져 있는 한 가치를 무한정 유지한다.

- 전기 노이즈(EMI), 방사선 등에 상대적으로 민감하지 않음

- DRAM보다 더 빠르고 더 비싸다

- Dynamic RAM (DRAM)

- 동적 램은 기록된 내용을 유지하기 위하여 주기적으로 재충전(Refresh)이 필요하다. 기본적으로 축전기(Capacitor)로 이루어지며 이것의 충전 상태로 정보를 기록한다. 계속 재충전해야 하는 이유는 캐퍼시터가 시간이 지나면 저절로 방전되기 때문이다

- 각 셀은 커패시터와 함께 비트를 저장한다. 접근을 위해 하나의 트랜지스터가 사용된다

- 값은 10-100ms마다 새로 refresh 해야 한다

- SRAM보다 장애(EMI, 방사선 등)에 더 민감하다

- SRAM보다 느리고 저렴하다

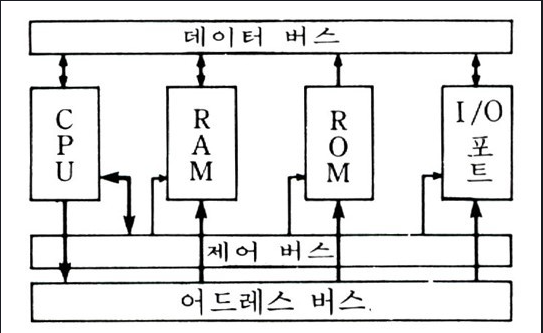

#Traditional CPU-Memory Bus Structure

BUS란 컴퓨터 내에서 데이터(data) 신호, 어드레스(address) 신호, 제어신호를 보내기 위한 신호선이 모여진 것으로 각각을 데이터 버스, 어드레스 버스, 제어 버스라고 한다. 쉽게 말해, 컴퓨터 내부의 회로에서, 중앙처리장치(CPU)와 주기억장치, 입출력장치간에 정보를 전송하는 데 공용으로 사용하는 전기적 통로이다

위에 사진처럼 BUS는 주소, 데이터 및 제어 신호를 전달하는 병렬 와이어의 집합이다. BUS는 일반적으로 여러 장치에 의해 공유된다.

#Memory Read Transaction (1)

CPU가 메모리 버스에 주소 A를 배치한다

#Memory Read Transaction (2)

메인 메모리는 메모리 버스에서 A를 읽고 단어 x를 검색하여 버스에 배치한다

#Memory Read Transaction (3)

CPU가 버스에서 단어 x를 읽고 레지스터 %eax에 복사한다

#Memory Write Transaction (1)

CPU는 A 주소를 버스에 배치한다. 기본 메모리는 읽고 해당 데이터 워드가 도착할 때까지 기다린다

#Memory Write Transaction (2)

CPU는 버스에 데이터 word y를 배치한다

#Memory Write Transaction (3)

메인 메모리는 버스에서 데이터 워드 y를 읽고 주소 A에 저장한다

#The Bigger Picture: I/O Bus

#Storage 트랜드

#The CPU-Memory Gap

가면갈수록 DRAM, 디스크 및 CPU 속도 간 격차가 더 커진다

#Locality

집약성 (Locality)의 원리: 프로그램이 최근에 사용한 주소에 가깝거나 동일한 주소를 가진 데이터와 명령을 사용하는 경향을 말한다. 그렇기 때문에 집약성이란 프로그램이 실행 도중 기억 장치를 참조하는 패턴이 기억 장치의 전 부분에 걸쳐 고루 나타나는 것이 아니라 어느 순간에는 일정한 한두 곳의 기억 장치 부분에 집중적으로 접근하는 성질이다

Temporal locality (잠정 구역성): 최초 참조된 기억 장소가 가까운 미래에도 계속 참조될 가능성이 높음을 의미한다

Spatial locality (공간적 구역성): 일단 하나의 기억 장소가 참조되면 그 근처의 기억 장소가 계속 참조되는 경향이 있는 성질. 배열 순례, 순차적 코드의 실행, 프로그래머들이 관련된 변수들을 서로 근처에 선언하는 경우 등에 장소 구역성이 나타난다

#예제

sum = 0;

for (i = 0; i < n; i++)

sum += a[i];

return sum;- 데이터 참조 (Data references)

- 배열 element 계속 참조 (stride-1 reference pattern) -> 공간적 구역성

- 각 iteration마다 변수 sum 참조 -> 잠정 구역성

- Instruction references

- 순서대로 instruction을 참조 -> 공간적 구역성

- 반복적으로 루프 순환 -> 잠정 구역성

#Taking Advantage of Locality

- 메모리 계층의 특성 사용 (large and slow vs small and fast)

- 디스크 또는 SSD(가상 메모리)에 모든 데이터 저장

- 최근 액세스한(및 인근) 항목을 디스크에서 더 작은 DRAM 메모리로 복사

- 더 최근에 액세스한(및 가까운) 항목을 DRAM에서 더 작은 SRAM 메모리로 복사

- 구역성은 여러 요인에 따라 달라진다

- 개발자의 데이터 구성 선택

- 개발자의 알고리즘 선택

- 개발자의 다른 코딩 결정

- 메모리 하드웨어 구성

- 개발자의 프로그래밍 언어 선택

- 또한 프로세스에 의해 나타나는 지역성은 실행 중에 변화하는 경향이 있다

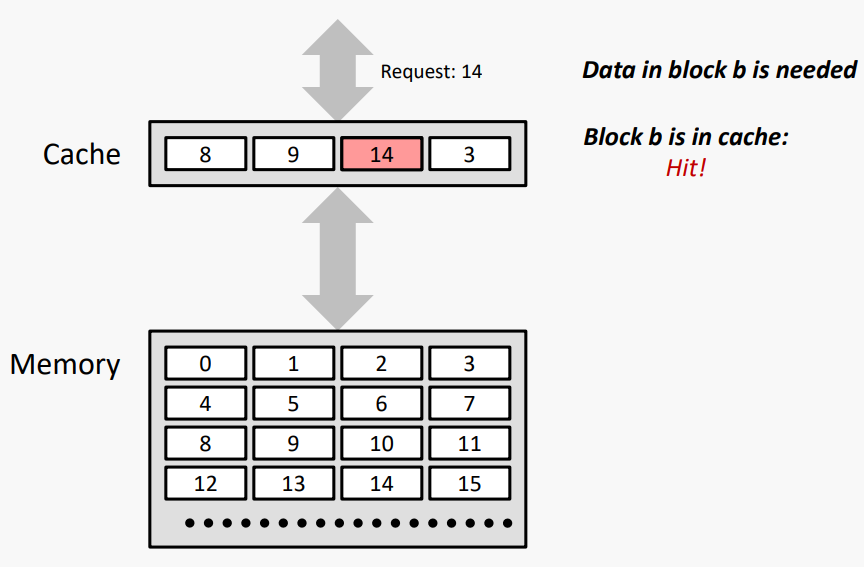

#Caches 캐시 (소형 고속 기억 장치)

캐시는 주기억 장치와 중앙처리장치 사이에 있는 데이터를 저장해두는 임시장소이다. 캐시는 주기억장치와 중앙처리장치 사이에 있는 고속 버퍼 메모리로, 기억 용량(memory capacity)은 주기억 장치에 비해 빨라서 데이터에 접근하기에 좋다는 장점이 있다. 캐시 메모리(cache memory) 또는 로컬 메모리(local memory) 라고도 한다.

다시 말해 더 크고 느린 장치에서 데이터의 하위 집합에 대한 준비 영역 역할을 하는 더 작고 빠른 저장 장치이다

기억 장치 계층의 기본 개념: 각 k에 대해, k레벨에서 더 빠르고 작은 장치는 k+1레벨에서 더 크고 느린 장치의 캐시 역할을 한다

- 메모리 계층이 작동하는 이유는 무엇일까?

- 구역성 때문에 프로그램은 level k+1의 데이터에 액세스하는 것보다 level k의 데이터에 액세스하는 빈도가 더 높은 경향이 있기 때문

- 따라서 레벨 k+1의 저장공간은 더 느릴 수 있고, 따라서 비트당 더 크고 저렴할 수 있다

메모리 계층은 하단 근처의 저렴한 스토리지만큼 비용이 많이 들지만 상단 근처의 빠른 스토리지 속도로 프로그램에 데이터를 제공하는 대용량 스토리지 풀을 생성한다

#기본 캐시 개념

#기본 캐시 개념: Hit

#기본 캐시 개념: Miss

#Types of Cache Misses

- Cold (compulsory) miss

- 캐시가 비어 있기 때문에 콜드 미스 발생

- 아니면 우리가 처음으로 무언가에 접근하고 있기 때문일수도 있음

- Conflict miss

- 대부분의 캐시는 레벨 k+1에 있는 블록을 레벨 k에 있는 블록 위치의 작은 부분 집합(때로는 싱글톤)으로 제한한다

- 예: 레벨 k+1의 블록 i는 레벨 k의 블록(i mod 4)에 배치되어야 한다

- Conflict misse은 level k 캐시가 충분히 크지만 여러 데이터 개체가 모두 동일한 level k 블록에 매핑될 때 발생한다

- 예: 블록 0, 8, 0, 8, 0, ...을 참조하면 매번 miss됨

- 대부분의 캐시는 레벨 k+1에 있는 블록을 레벨 k에 있는 블록 위치의 작은 부분 집합(때로는 싱글톤)으로 제한한다

- Capacity miss

- 활성 캐시 블록 집합(작업 집합)이 캐시보다 클 때 발생

#Examples of Caching in the Hierarchy

#Cache Memories

- 캐시 메모리는 하드웨어에서 자동으로 관리되는 작고 빠른 SRAM 기반 메모리이다

- 자주 액세스하는 기본 메모리 블록 보유

- CPU는 캐시(예: L1, L2, L3)에서 데이터를 먼저 찾은 다음 메인 메모리에서 데이터를 찾는다

일반적인 캐시 메모리 시스템 구조:

'Computer Science > Computer Organization' 카테고리의 다른 글

| [Lecture 19] Virtual Memory: Hardware and Performance (1) | 2022.11.12 |

|---|---|

| [Lecture 16] Cache Memory (0) | 2022.11.11 |

| [Lecture 14] Pipeline Handling Branches (0) | 2022.11.10 |

| [Lecture 8] Computer Performance (0) | 2022.11.09 |